FOPLP是面板進軍半導體的契機

先探投資週刊

面板產業已進入紅海時代,不過若擁有扇出型面板級封裝技術,將可有效運用閒置產能,並跨入半導體業務領域。

【文/黃俊超】

護國神山台積電之於台股,也代表著半導體產業之於台灣經濟,上下游搭配得宜,台積電創辦人張忠謀曾經說過,台灣半導體擁有三大優勢,一是人才,大量高品質的工程師;二是人才流動率低,以台積電為例每年離職率僅約四~五%,遠低於美國七○、八○年代晚期的十五~二○%,培養人才必須耗費數年時間,流動率若超過十%怎能做出好成績;三是交通方便,高鐵、高速公路通勤迅速。

先進封裝需求高速成長

台灣不僅在晶圓製造領域具有絕對高度優勢,在半導體封裝同樣也擁有領先地位,不過也須留意,根據IDC研究報告顯示,考量地緣政治、技術發展、人才與成本影響,整合元件製造廠(IDM)加速轉向東南亞市場,封測業者也跟進,尤其馬來西亞與越南,預計二○二七年東南亞半導體封裝測試市占率將達十%,台灣占比由二二年的五一%下滑至四七%。

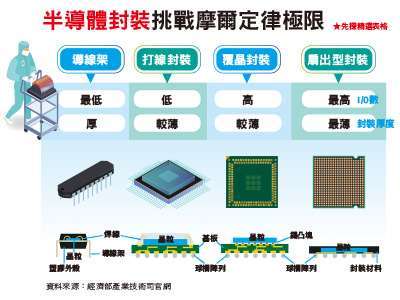

一般來說,封裝技術應該是以密度作為區分,成本高低與其效能成正比,不過由於每一種電子產品,所對應的成本效益考量,以及應用範圍並不相同,如消費性、工業用或企業規模,而非是孰優孰劣,因此,廠商會選擇最適當的封裝方式,而非一昧的只追求最先進的封裝技術,且在各技術之間也並非是互相取代的關係。

晶片大廠 Intel 創始人之一高登摩爾提出的摩爾定律,積體電路上可容納電晶體數目,約每隔兩年便增加一倍,時至今日,半導體先進製程已來到二奈米,甚至來到一.四奈米或一奈米,後段載板配線精密度也需要跟著提升。由於單一晶片電晶體密度逐漸逼近極限,也使得異質整合概念迅速發展,將不同的晶片透過封裝、堆疊技術整合,進而衍生出各種先進封裝技術。

先進封裝最受市場矚目的是 CoWoS,目前仍是供不應求。CoWoS 可以分開來看,CoW(Chip-on-Wafer)指的是晶片堆疊,WoS 則是(Wafer-on-Substrate)即晶片堆疊在基板上,將晶片堆疊後封裝於基板上,根據排列的形式,分為 2.5D 與 3D,不僅可以減少晶片所需的空間,也有效減少功耗,藉此達到加速運算但成本仍是可控的目標。

全球晶片應用端變化和轉型,是推動先進封裝產業發展的動力,根據研調機構 Yole 預估,全球先進封裝市場規模,將由二○二二年的四四三億美元,成長至二八年的七八六億美元,年複合成長率為十.六%,而另一方面,傳統晶片封裝市場二二年規模為四七五億美元,預計二八年成長至五七五億美元,也就是至二八年,整體晶片封裝市場預計將會達到一三六○億美元。台積電不僅致力於 CoWoS,也是扇出型封裝市場的主導者之一。

FOPLP 具產能與成本優勢

Yole 也曾預估,全球扇出型封裝市場二○二○~二六年複合成長率將達十五.一%。整合扇出型封裝是業界研發出相稱的IC封裝技術,根據經濟部產業技術司資料顯示,以晶圓級扇出型封裝(FOWLP)為主,不過因所使用的晶圓設備尺寸,導致製程基板面積受限,經濟部專案支持工研院研發以扇出型封裝為基礎,進一步發展出扇出型面板級封裝(FOPLP)技術。

扇出型封裝異質整合各類晶片,並將被動元件或功率器件(power device)嵌入其中,再以微細銅重佈線路層(RDL)互連形成一個小型化的解決方案,兩個技術各具有適合的應用領域。目前主要應用於車用電子,如功率器件、感測器、通信和計算控制晶片等,也朝向 5G/AI、資料中心、穿戴裝置、電源管理晶片、射頻收發器等各種應用發展。(全文未完)

來源:《先探投資週刊》2297 期

更多精彩內容請至 《先探投資週刊》

- 免費體驗5萬美元模擬交易 投資全球資產

- 掌握全球財經資訊點我下載APP

- 講座

- 公告

下一篇