解密先進封裝技術

先探投資週刊

先進封裝大部分是利用「晶圓廠」的技術,直接在晶圓上進行,由於這種技術更適合晶圓廠來做,因此台積電大部分的先進封裝都是自己做的。

【文/曲建仲】

縮小電晶體的製程節點(七奈米、五奈米、三奈米)可以縮小晶片(Chip),縮小晶片可以縮小印刷電路板(Printed Circuit Board; PCB),而縮小印刷電路板就可以縮小電子產品的尺寸,因此製程節點是朝向愈來愈小的方向發展,但是先進製程發展到三奈米以下開始接近極限,一般認為「極紫外光」(Extreme Ultraviolet; EUV)的極限是一奈米,因此一奈米以下的製程發展會遇到瓶頸,該怎麼辦呢?

什麼是系統單封裝(System in a Package; SiP)?

將數個功能不同的晶片(Chip)直接封裝成具有完整功能的「一個」積體電路(Integrated Circuit; IC),稱為「系統單封裝」(System in a Package; SiP)。例如:將手機的處理器與記憶體(Double Data Rate SDRAM; DDR)封裝在一起,此時仍然是兩個獨立的晶片,只是封裝在同一個外殼而已,比發展先進製程更簡單,在某些特別的應用上甚至可以將被動元件、連接器、天線等一起封裝進去,先進封裝就是一種系統單封裝技術。

先進封裝的前段與後段

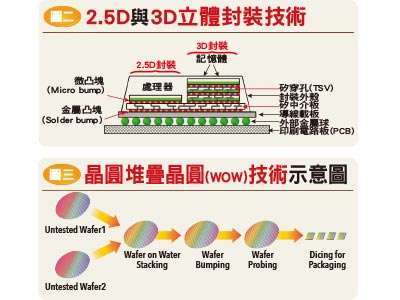

先進封裝是指使用左右水平或上下垂直的方法將晶片堆疊起來,同時縮小積體電路的一種技術,可以再細分為前段與後段,如圖一所示。

立體封裝前段(3D Front End; 3DFE):也就是積體電路內部的晶片堆疊技術,如何把許多晶片堆疊起來?又可以分為「晶片堆疊晶圓」(Chip on Wafer; CoW)與「晶圓堆疊晶圓」(Wafer on Wafer; WoW)兩種。

立體封裝後段(3D Back End; 3DBE):也就是積體電路外部的導線分布技術,如何分布導線才方便接下來和印刷電路板(PCB)連接。

傳統的封裝都是在「封裝廠」中進行,有點像是傳統的精密機械工業,但是先進封裝大部分是利用「晶圓廠」的技術直接在晶圓上進行,由於這種技術更適合晶圓廠來做,因此台積電大部分的先進封裝都是自己做的。(全文未完)全文及圖表請見《先探投資週刊 2130+2131 合刊號精彩當期內文轉載》

來源:《先探投資週刊》2130+2131 合刊號

更多精彩內容請至 《先探投資週刊》

- 掌握全球財經資訊點我下載APP

延伸閱讀

- 講座

- 公告

上一篇

下一篇