談先進封裝技術 台積電:系統整合是未來主流路線之一

鉅亨網記者林薏茹 台北 2020-07-02 07:30

晶圓代工龍頭台積電 (2330-TW) 研究發展組織系統整合技術副總余振華表示,SiP 技術對速度、功耗改善空間有限,而 Chiplet 封裝技術則能維持每顆晶片效能、成本更低,加上 5G、AI 應用對性能要求嚴苛,看好這類「系統整合」技術,將成半導體技術主流路線之一。

根據陸媒報導,余振華出席 SEMICON China 2020 的中國國際半導體技術大會 CSTIC 2020,分享讓摩爾定律延續的三大先進封裝技術,包括整合型扇出 InFO、2.5D 的 CoWoS、3D IC,及 Chiplet 小晶片趨勢。

余振華在 SEMICON China 2020 上,以「Next Big Frontiers:Chiplet Integrations and More」為題,談及 SiP(System in a Package) 技術,余振華解釋,SiP 是把 2 至 3 顆晶片封裝在一起,將幾個小晶片封裝成一顆大晶片,嚴格來說,不是一個成功的技術,現在已很少人提起。

對於近期熱門的 Chiplet 封裝技術,余振華指出,Chiplet 概念就是把一顆 SoC 分成好幾個晶片,維持每顆晶片效能,但成本可以更低,是 SoP(System on Packaging) 的概念,類似 SiP 概念,但其實不同。

余振華指出,由於摩爾定律遭遇的瓶頸越來越多,「超越摩爾定律」、「後摩爾定律」概念越來越重要。在「後摩爾定律」時代,是將原本封裝在一顆晶片中的功能,拆成好幾個晶片後再整合,這種系統整合技術,開始成為半導體技術的主流路線之一。

余振華並說,另一個原因是 AI 與 5G 已成半導體產業最大推手,但對性能要求嚴苛,且為縮減體積,也開始朝系統整合技術努力。

陸媒表示,余振華最著名為其領軍的整合連接與封裝部門,成功研發出高階封裝技術 InFO(整合扇出型封裝) 與和 2.5D CoWoS(Chip on Wafer on Substrate) 技術,讓台積電一路獨拿蘋果 iPhone 處理器訂單,也因在高階封裝技術上取得成功,讓蘋果 iPhone 處理器從此離不開台積電製程技術。

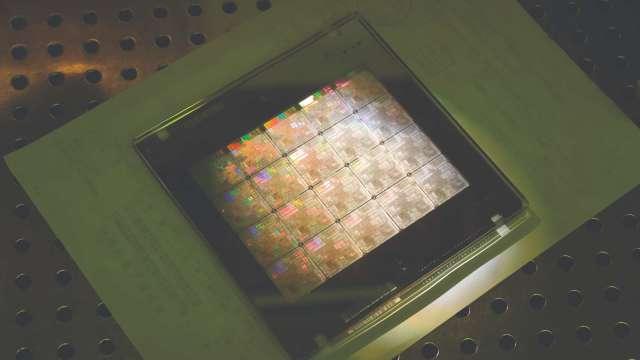

台積電在先進封裝技術方面,目前除既有的整合型扇出 InFO 技術,及 2.5D 的 CoWoS,也已發展出晶圓級封裝技術系統整合晶片 (TSMC-SoIC) 技術。

- 安全可靠的多資產平台!靈活槓桿 免費模擬

- 掌握全球財經資訊點我下載APP

上一篇

下一篇